PCB Panelization 가이드: SMT 수율을 높이는 V-Cut·Tab Routing 기준

PCB Panelization은 단순히 여러 보드를 한 장에 붙이는 작업이 아닙니다. SMT 조립, 디패널링, 보드 휨, 테스트 접근성, 물류 비용과 fixture 안정성까지 함께 결정해 수율 리스크를 낮추는 양산 설계 포인트입니다.

Hommer Zhao

· 창립자 & 기술 전문가

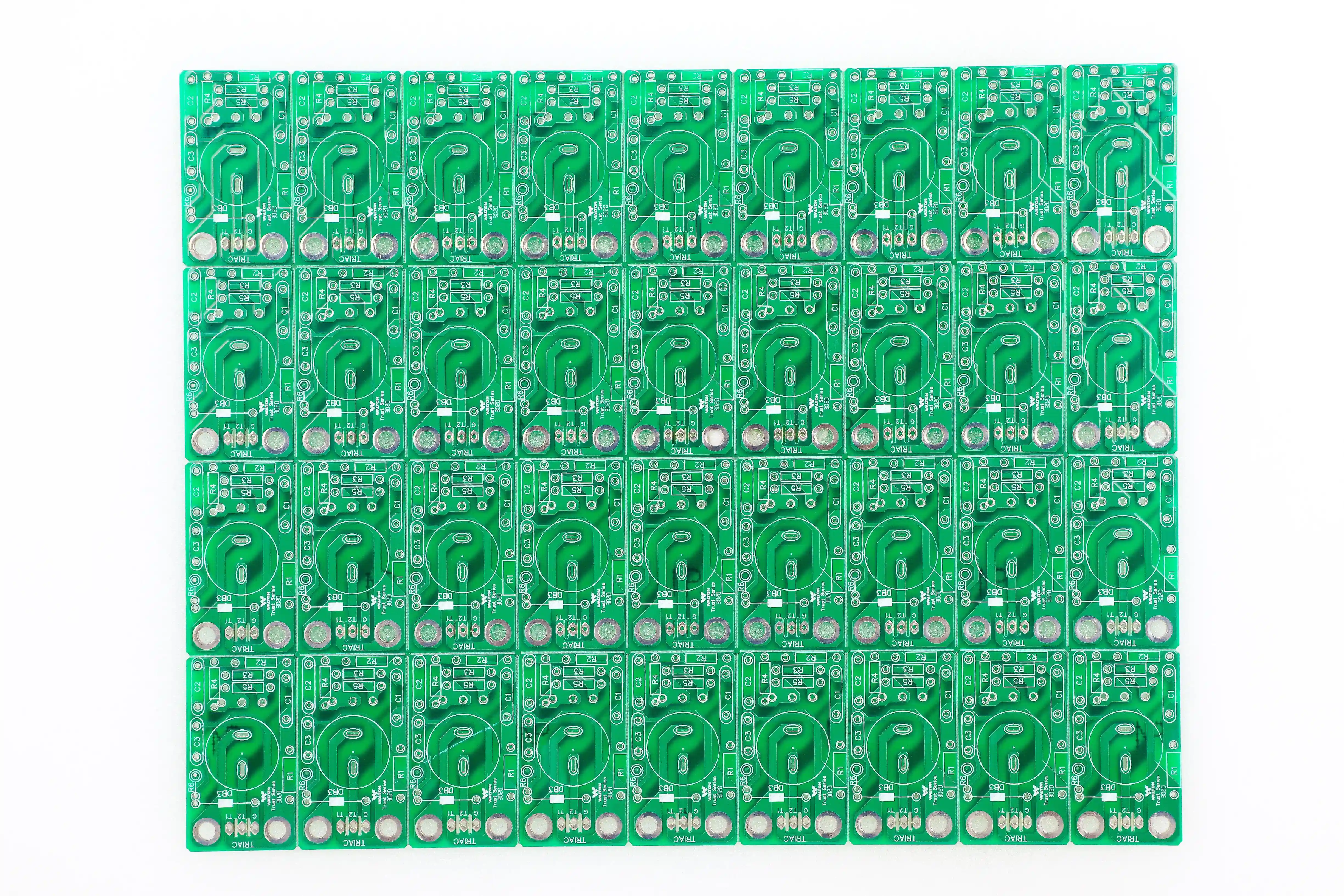

PCB panelization은 작은 보드를 생산 패널 안에 배치하는 작업이지만, 실제 영향은 훨씬 넓습니다. 같은 회로도와 같은 BOM이라도 panel rail, V-cut, tab routing, fiducial, tooling hole, breakaway 위치가 맞지 않으면 SMT 인쇄 안정성, pick and place 반복성, reflow 후 휨, AOI 접근성, 최종 디패널링 불량이 모두 흔들릴 수 있습니다. 특히 한국 고객이 많이 요청하는 빠른 NPI와 소량 반복 생산에서는 패널 설계를 초기에 제대로 잡는 것이 재제작 비용을 줄이는 가장 현실적인 방법입니다.

이 글은 PCB assembly, SMT assembly, PCB manufacturing을 한 번에 운영할 때 panelization을 어떻게 검토해야 하는지 정리합니다. 단품 외형을 생산 패널로 바꾸는 순간부터 보드는 더 이상 전기 설계 파일만의 문제가 아니라 장비, 공정, 검사, 포장, 물류가 함께 움직이는 제조 패키지가 됩니다.

기본 개념은 printed circuit board, surface-mount technology, 그리고 전자 조립 품질 기준의 배경이 되는 IPC electronics standards를 함께 보면 이해가 쉽습니다.

“Panelization은 CAM 엔지니어만의 일이 아닙니다. 5mm rail, 3개 fiducial, 0.5mm V-cut web 같은 작은 숫자가 SMT 수율과 디패널링 스크랩률을 동시에 바꿉니다. 저는 NPI 단계에서 패널 도면을 BOM만큼 중요하게 봅니다.”

— Hommer Zhao, 창립자 & 기술 전문가

SMT 장비와 컨베이어를 고려한 일반 panel rail 검토 범위

패널 기준 fiducial을 최소 3점으로 관리하는 실무 기준

V-cut residual thickness 검토가 자주 걸리는 구간

PCB 제작성과 조립성을 함께 보는 DFM/DFA 검토

Panelization을 단품 외형 복사로 보면 안 되는 이유

단품 PCB는 회로와 외형을 만족하면 끝나는 것처럼 보입니다. 그러나 생산 라인에서는 보드를 잡고, 이동하고, 인쇄하고, 실장하고, 리플로우하고, 검사한 뒤 분리해야 합니다. 이 모든 단계는 단품이 아니라 패널 기준으로 움직입니다. 패널 강성이 약하면 stencil printing 중 중앙부가 처지고, 부품이 가장자리까지 붙어 있으면 conveyor clamp나 support pin이 간섭될 수 있습니다.

또한 panel utilization만 높이려다 보드 간격을 너무 줄이면 디패널링 때 edge crack, solder joint stress, ceramic capacitor cracking이 생길 수 있습니다. 반대로 여백을 과도하게 주면 PCB 단가는 올라가고 SMT 한 사이클당 생산량은 줄어듭니다. 그래서 panelization은 비용 절감과 공정 안정성 사이의 균형입니다.

V-Cut과 Tab Routing은 어떻게 선택하나

가장 흔한 선택은 V-cut과 tab routing입니다. V-cut은 직선 외형, 사각 보드, 높은 반복 생산에 유리합니다. 분리 속도가 빠르고 단가가 낮은 편이지만, 곡선 외형이나 edge 가까운 부품에는 불리합니다. V-groove 라인을 따라 잔여 두께가 남기 때문에 분리 순간의 굽힘 응력이 보드 전체에 전달될 수 있습니다.

Tab routing은 복잡한 외형, 원형 보드, 커넥터 cutout, edge 부품이 많은 보드에 유리합니다. 마우스 바이트나 routed slot으로 단품을 잡아 두기 때문에 외형 자유도가 높지만, 탭 위치와 개수, hole pitch, burr 관리가 중요합니다. 최종 제품이 인클로저에 들어가면 탭 잔여부가 간섭을 만들 수 있으므로 조립 도면에서 허용 burr 높이를 숫자로 정해야 합니다.

| 방식 | 적합한 보드 | 장점 | 대표 리스크 | 실무 기준 |

|---|---|---|---|---|

| V-Cut | 직선 외형, 사각 보드, 대량 생산 | 분리 속도 빠름, 비용 효율 높음 | edge 부품 응력, 곡선 외형 대응 어려움 | 부품을 V-cut 라인에서 3~5mm 이상 띄워 검토 |

| Tab Routing | 복잡한 외형, 커넥터 cutout, 원형 보드 | 외형 자유도 높고 응력 위치 제어 가능 | burr, 탭 잔여부, 라우팅 시간 증가 | 탭 폭과 mouse bite pitch를 도면에 명시 |

| Hybrid | 일부 직선, 일부 불규칙 외형 | 비용과 외형 대응의 균형 | 분리 순서가 복잡해질 수 있음 | 작업 지침서에 분리 방향과 순서 포함 |

| Carrier Panel | FPC, rigid-flex, 아주 작은 PCB | SMT 핸들링과 평탄도 보조 | 보강재, 접착, 열팽창 관리 필요 | 조립 fixture와 함께 승인 |

| Single-Up | 큰 보드, 무거운 부품, 낮은 수량 | 디패널링 리스크 최소화 | SMT 생산성 저하, setup 비용 부담 | NPI 5~20장에서는 합리적일 수 있음 |

Panel Rail은 몇 mm가 적절한가

Panel rail은 장비가 패널을 잡고 이동시키는 여유 영역입니다. 일반적으로 5~10mm 범위에서 검토하지만, 절대값 하나로 결정하면 안 됩니다. 보드 크기, 두께, 장비 clamp 구조, bottom-side 부품 유무, wave 또는 selective soldering fixture 사용 여부에 따라 달라집니다. 양면 SMT에서 bottom side 부품이 가장자리 가까이에 있으면 rail을 더 넓게 잡거나 carrier support를 검토해야 합니다.

Rail에는 fiducial, tooling hole, barcode, panel ID, process coupon을 배치할 수도 있습니다. 다만 rail을 너무 많은 정보의 보관 장소로 쓰면 support pin과 clamp가 간섭될 수 있으므로 실제 장비 기준으로 배치해야 합니다. 품질 추적성이 필요한 제품은 rail 제거 전에 패널 ID와 단품 serial ID 매핑이 기록되는지도 확인해야 합니다.

“Panel rail을 2mm 줄여 PCB 원가를 낮춘 것처럼 보였지만, 실제로는 stencil support가 불안정해져 첫 양산에서 2% 이상 solder bridge가 늘어난 사례가 있습니다. 패널 원가는 항상 SMT cycle time과 불량 비용까지 같이 계산해야 합니다.”

— Hommer Zhao, 창립자 & 기술 전문가

Fiducial과 Tooling Hole 설계

Fiducial은 pick and place와 AOI가 좌표계를 잡는 기준입니다. 단품 fiducial만 있고 panel fiducial이 없으면 장비가 패널 전체의 회전과 늘어짐을 안정적으로 보정하기 어렵습니다. 실무에서는 패널 기준 3점 이상, 단품 기준 2점 이상을 검토하는 경우가 많고, solder mask clearance와 copper keepout을 함께 둡니다.

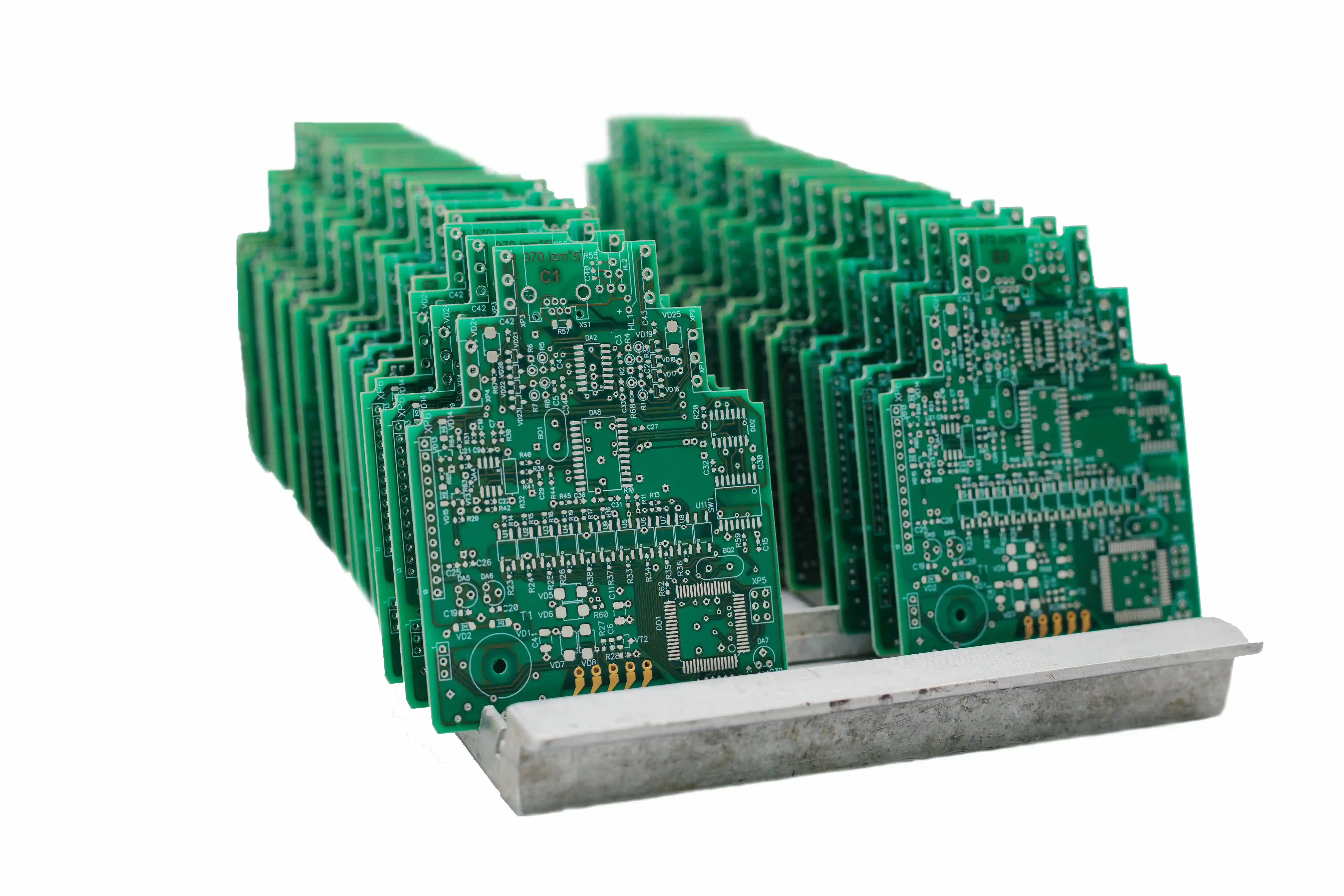

Tooling hole은 fixture, 라우터, 테스트 지그, 선택 납땜 팔레트와 연결됩니다. 위치가 단순히 빈 공간에 찍힌 구멍이면 안 됩니다. 라우팅 방향, panel stiffness, test access, 최종 분리 순서와 맞아야 합니다. 특히 PCB testing services나 기능 테스트 지그가 포함되면 tooling 기준을 초기에 공유해야 fixture 수정 비용을 줄일 수 있습니다.

SMT 조립성 관점의 Panelization 체크포인트

Panelization을 DFM 파일로만 보면 copper spacing, drill, outline 같은 제작 이슈에 치우치기 쉽습니다. 하지만 PCBA 수율을 위해서는 DFA까지 봐야 합니다. 가장자리 부품 간격, tall component 방향, bottom-side 부품 보호, solder paste printing support, reflow carrier 필요 여부, AOI 카메라 접근성을 모두 검토해야 합니다.

예를 들어 heavy connector가 한쪽에 몰려 있으면 reflow 중 패널이 기울거나 휠 수 있습니다. 큰 알루미늄 전해 커패시터, transformer, shield can, 고전류 단자는 단품에서는 문제가 없어도 패널 배열이 반복되면서 무게 중심 문제가 커질 수 있습니다. 이런 경우 배열 방향을 바꾸거나 패널 내 보드 수를 줄이는 편이 전체 수율에는 더 유리할 수 있습니다.

NPI 전에 확인할 패널 설계 질문

- Panel rail 폭이 실제 SMT 장비 clamp와 conveyor 조건에 맞는가

- Panel fiducial 3점과 단품 fiducial이 모두 명확한가

- V-cut 또는 tab 위치가 MLCC, BGA, connector solder joint에 응력을 주지 않는가

- Bottom-side 부품이 support pin, wave pallet, test fixture와 간섭하지 않는가

- 디패널링 후 burr 허용 기준과 외형 공차가 조립 도면에 숫자로 적혀 있는가

- 패널 ID, 단품 serial, test result를 연결할 추적성 규칙이 있는가

디패널링 공정과 품질 리스크

디패널링은 마지막 단계처럼 보이지만, 잘못하면 완성된 PCBA를 손상시키는 공정입니다. 수동 breakaway는 빠르고 저렴하지만 응력 관리가 약합니다. V-cut separator는 반복성이 좋지만 보드 크기와 부품 위치 제약이 있습니다. Router depaneling은 외형 품질이 좋고 응력 제어가 쉽지만, cycle time과 fixture 비용이 증가합니다.

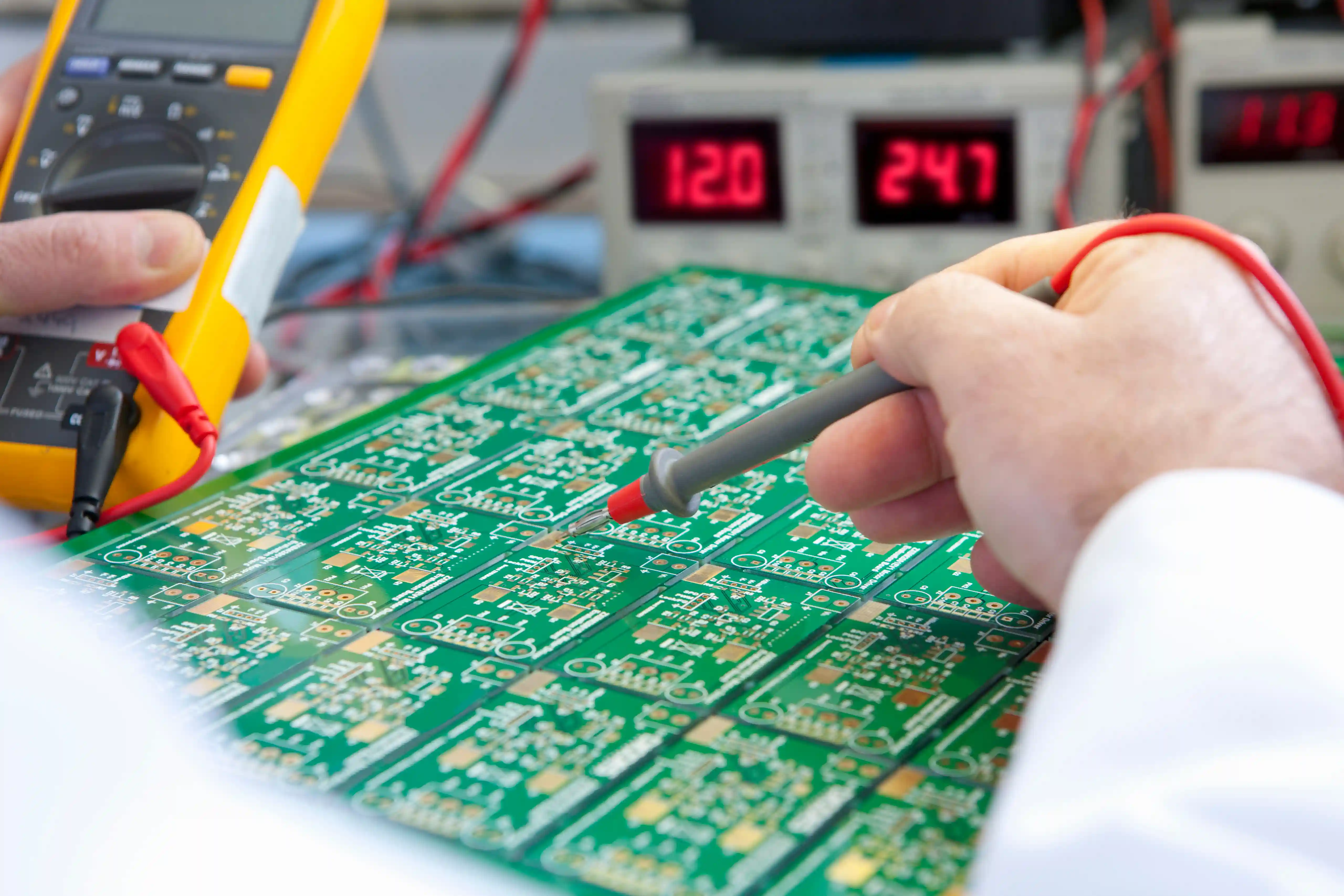

민감한 제품은 디패널링 후 검사 항목을 별도로 둬야 합니다. Edge crack, copper exposure, burr, solder joint crack, nearby MLCC crack, connector looseness를 샘플링으로 확인하고, 필요하면 cross-section이나 dye-and-pry까지 검토합니다. 자동차, 의료, 산업 제어 제품에서는 이 단계의 작은 크랙이 현장 진동과 열 사이클에서 큰 고장으로 이어질 수 있습니다.

Panelization과 테스트 전략은 함께 설계해야 한다

ICT, flying probe, functional test를 어떻게 할지도 panelization에 영향을 줍니다. 패널 상태에서 테스트할 것인지, 단품으로 분리한 뒤 테스트할 것인지에 따라 test point 위치, fixture pin 접근성, barcode 전략, fail unit 처리 방식이 달라집니다. 패널 상태 테스트는 처리량이 좋지만, fail unit만 선별하기 위한 표시와 재작업 흐름이 필요합니다.

관련 전략은 Flying Probe vs ICT 가이드와 Functional Test Fixture 가이드에서 더 자세히 다루지만, 핵심은 같습니다. 테스트는 생산 후에 붙이는 별도 단계가 아니라, panelization 단계에서 이미 공간과 기준점을 확보해야 하는 제조 설계 요소입니다.

패널 효율과 총제조비용을 함께 계산해야 한다

Panelization 검토에서 자주 나오는 질문은 “한 패널에 몇 장을 넣을 수 있나요”입니다. 이 질문은 중요하지만 충분하지 않습니다. 패널당 단품 수가 늘면 PCB 원가는 낮아질 수 있지만, SMT line에서 패널이 너무 크거나 무거워지면 handling, reflow profile, AOI cycle time, 디패널링 시간이 증가합니다. 즉 unit PCB cost만 낮아지고 실제 PCBA 총비용은 올라갈 수 있습니다.

예를 들어 4-up 패널과 6-up 패널을 비교할 때 단순 면적 효율은 6-up이 좋아 보일 수 있습니다. 하지만 6-up에서 패널 휨이 커져 solder bridge와 AOI false call이 늘거나, router depaneling이 1패널당 40초에서 70초로 늘면 전체 생산성은 기대와 달라집니다. 반복 양산에서는 패널 효율, SMT cycle time, 검사 시간, 불량률, 포장 단위까지 한 표에 놓고 판단해야 합니다.

소량 생산에서는 다른 계산이 필요합니다. 20장 이하 NPI에서 과도하게 복잡한 panelization을 만들면 CAM 검토, fixture, stencil 수정 시간이 오히려 납기를 늦출 수 있습니다. 반대로 500장 이상 반복 생산이 예정되어 있으면 초기에 1~2일을 투자해 패널 방향과 디패널링 fixture를 승인하는 편이 반복 주문마다 비용을 줄입니다. 그래서 좋은 RFQ는 수량 1개만 묻지 않고 EVT, DVT, PVT, 양산 예상 수량을 함께 확인합니다.

“테스트 포인트가 단품에서는 보이는데 패널 fixture에서는 rail이나 탭 때문에 접근이 안 되는 경우가 있습니다. 그래서 저는 패널 승인 전에 Gerber, CPL, 테스트 포인트 목록, 디패널링 방향을 한 번에 겹쳐 봅니다. 30분 검토가 fixture 재가공 3일을 막습니다.”

— Hommer Zhao, 창립자 & 기술 전문가

FAQ

PCB panel rail은 보통 몇 mm로 잡나요?

일반 SMT 조립에서는 5~10mm 범위를 자주 검토합니다. 다만 장비 clamp, board thickness, bottom-side 부품, barcode, tooling hole 요구에 따라 3mm로도 충분한 경우가 있고 10mm 이상이 필요한 경우도 있습니다. NPI에서는 실제 장비 기준으로 확인하는 것이 가장 안전합니다.

V-cut 라인 가까이에 부품을 얼마나 띄워야 하나요?

보수적으로는 3~5mm 이상을 먼저 검토합니다. 특히 MLCC, BGA, fine-pitch connector, crystal처럼 응력에 민감한 부품은 V-cut 라인 가까이에 두지 않는 편이 좋습니다. 고객 외형 제약 때문에 피할 수 없으면 router depaneling이나 tab routing을 검토합니다.

Panel fiducial은 몇 개가 필요하나요?

패널 기준으로 최소 3개를 두는 방식이 실무적으로 안정적입니다. 단품 fiducial 2개만으로도 일부 장비는 동작하지만, 패널 전체의 회전과 스케일 변화를 보정하려면 panel fiducial이 필요합니다. Fiducial 주변에는 solder mask clearance와 copper keepout을 함께 둬야 합니다.

Tab routing의 mouse bite hole 크기는 어떻게 정하나요?

제품 두께와 외형 품질 요구에 따라 달라지지만, hole diameter, pitch, tab width를 조립 도면에 숫자로 명시해야 합니다. 예를 들어 1.6mm FR-4 보드와 0.8mm 보드는 같은 탭 설계를 쓰면 분리력과 burr가 다르게 나올 수 있습니다. 최종 하우징 간섭이 있으면 burr 허용 높이도 지정해야 합니다.

소량 시제품도 panelization이 필요한가요?

5~20장 수준의 단순 보드는 single-up으로도 충분할 수 있습니다. 그러나 0201, BGA, 양면 SMT, 자동 AOI, 기능 테스트 fixture가 들어가면 소량이라도 패널 기준이 필요합니다. 시제품에서 패널을 제대로 잡으면 200장, 2,000장 양산 이관 시 fixture와 stencil을 다시 만드는 일을 줄일 수 있습니다.

Panelization은 PCB 제조사가 알아서 해도 되나요?

기본 CAM 패널은 제조사가 제안할 수 있지만, SMT 조립과 디패널링 조건까지 알지 못하면 완전하지 않습니다. BOM, CPL, 부품 높이, edge connector, 테스트 포인트, 최종 인클로저 제약을 함께 공유해야 합니다. 특히 IPC Class 3 수준 제품이나 자동차용 보드는 고객 승인 패널 도면을 남기는 편이 좋습니다.

결론

좋은 PCB panelization은 한 패널에 몇 장을 넣을지 정하는 계산이 아닙니다. 제작성, 조립성, 검사성, 디패널링 응력, 추적성, 물류 비용을 함께 정리하는 제조 설계입니다. V-cut과 tab routing, rail 폭, fiducial, tooling hole, 테스트 접근성을 초기 DFM/DFA에서 함께 잡으면 초도 수율과 양산 전환 속도가 눈에 띄게 안정됩니다.

WellPCB Korea는 prototype PCB부터 turnkey assembly, box build까지 이어지는 프로젝트에서 패널 설계와 조립 공정을 함께 검토합니다. Gerber, BOM, CPL, 조립 도면, 목표 수량을 보내주시면 문의 페이지 또는 온라인 문의 폼을 통해 panelization 리스크와 개선 방향을 빠르게 검토할 수 있습니다.

작성자 소개

Hommer Zhao

창립자 & 기술 전문가

20년 이상의 PCB 및 전자 제조 경험을 보유한 WellPCB의 창립자입니다. 글로벌 고객에게 최적의 EMS 솔루션을 제공하기 위해 기술과 품질에 대한 깊은 통찰력을 공유합니다.

LinkedIn 프로필 보기관련 글

PCB 조립

SMT DFM 체크리스트: PCB 조립 전 반드시 잡아야 할 11가지 생산 리스크와 NPI 기준

SMT DFM은 Gerber 오류 찾기가 아니라 실제 조립 라인에서 멈출 리스크를 줄이는 release gate입니다. 패드, 스텐실, 패널, fiducial, 검사, 테스트 포인트까지 NPI 전에 확인할 기준을 실무적으로 정리합니다.

PCB 조립

Press-Fit 커넥터 조립 가이드: Hole 공차, 삽입 하중, Backplane PCB 양산에서 무엇이 중요할까

Press-fit connector assembly는 납땜 없이 고신뢰 접속을 구현하지만 finished hole 공차와 insertion force 관리가 수율을 좌우합니다. 이 글은 backplane PCB 양산에서 press-fit 조립을 안정화하는 핵심 기준을 정리합니다.

PCB 조립

PCB Functional Test Fixture 가이드: FCT 커버리지, 지그 설계, NPI에서 양산 이관까지

Functional test fixture는 전원이 들어간 제품의 실제 동작을 검증하는 마지막 방어선입니다. 이 글은 ICT와의 역할 구분, pogo pin 지그 설계, FCT 커버리지, NPI에서 양산 이관 기준을 PCB assembly 관점에서 정리합니다.